## **NPT Series N-Channel IGBT** with Anti-Parallel Hyperfast **Diode**

43 A, 1200 V

## HGTG11N120CND

The HGTG11N120CND is a Non- Punch Through (NPT) IGBT design. This is a new member of the MOS gated high voltage switching IGBT family. IGBTs combine the best features of MOSFETs and bipolar transistors. This device has the high input impedance of a MOSFET and the low on-state conduction loss of a bipolar transistor. The IGBT used is the development type TA49291. The Diode used is the development type TA49189.

The IGBT is ideal for many high voltage switching applications operating at moderate frequencies where low conduction losses are essential, such as: AC and DC motor controls, power supplies and drivers for solenoids, relays and contactors.

Formerly Developmental Type TA49303.

#### **Features**

- 43 A, 1200 V,  $T_C = 25^{\circ}C$

- 1200 V Switching SOA Capability

- Typical Fall Time: 340 ns at  $T_J = 150^{\circ} C$

- Short Circuit Rating

- Low Conduction Loss

- Thermal Impedance SPICE Model www.onsemi.com

- This is Pb-Free Device

#### ON Semiconductor®

www.onsemi.com

TO-247-3LD **CASE 340CK**

#### MARKING DIAGRAMS

\$Y = ON Semiconductor Logo &Z = Assembly Plant Code &3 = Data Code (Year & Week) &K = 1 ot

11N120CND = Specific Device Code

#### ORDERING INFORMATION

| Part Number   | Package | Brand     |

|---------------|---------|-----------|

| HGTG11N120CND | TO-247  | 11N120CND |

NOTE: When ordering, use the entire part number.

## ABSOLUTE MAXIMUM RATINGS (T<sub>C</sub> = 25°C, Unless Otherwise Specified)

| Description                                                                                      | Symbol                                | HGTG11N120CND  | Units     |

|--------------------------------------------------------------------------------------------------|---------------------------------------|----------------|-----------|

| Collector to Emitter Voltage                                                                     | BV <sub>CES</sub>                     | 1200           | V         |

| Collector Current Continuous  At $T_C = 25^{\circ}C$ At $T_C = 110^{\circ}C$                     | I <sub>C25</sub><br>I <sub>C110</sub> | 43<br>22       | A<br>A    |

| Collector Current Pulsed (Note 1)                                                                | I <sub>CM</sub>                       | 80             | Α         |

| Gate to Emitter Voltage Continuous                                                               | $V_{GES}$                             | ±20            | V         |

| Gate to Emitter Voltage Pulsed                                                                   | $V_{GEM}$                             | ±30            | V         |

| Switching Safe Operating Area at T <sub>J</sub> = 150°C (Figure 2)                               | SSOA                                  | 55 A at 1200 V |           |

| Power Dissipation Total at $T_C = 25^{\circ}C$<br>Power Dissipation Derating $T_C > 25^{\circ}C$ | P <sub>D</sub>                        | 298<br>2.38    | W<br>W/°C |

| Operating and Storage Junction Temperature Range                                                 | T <sub>J</sub> , T <sub>STG</sub>     | -55 to 150     | °C        |

| Maximum Lead Temperature for Soldering                                                           | TL                                    | 260            | °C        |

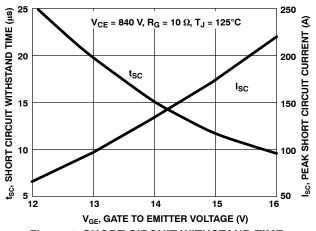

| Short Circuit Withstand Time (Note 2) at V <sub>GE</sub> = 15 V                                  | t <sub>SC</sub>                       | 8              | μs        |

| Short Circuit Withstand Time (Note 2) at V <sub>GE</sub> = 12 V                                  | t <sub>SC</sub>                       | 15             | μs        |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Pulse width limited by maximum junction temperature.

2. V<sub>CE(PK)</sub> = 840 V, T<sub>J</sub> = 125°C, R<sub>G</sub> = 10  $\Omega$ .

## **ELECTRICAL SPECIFICATIONS** (T<sub>J</sub> = 25, °C Unless Otherwise Specified)

| Parameter                                 | Symbol               | Test Co                                                                                                                           | onditions                             | Min  | Тур  | Max  | Units |

|-------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|------|------|-------|

| Collector to Emitter Breakdown<br>Voltage | BV <sub>CES</sub>    | $I_C = 250 \mu A, V_{GE} = 0 V$                                                                                                   |                                       | 1200 | -    | -    | V     |

| Collector to Emitter Leakage Current      | I <sub>CES</sub>     | V <sub>CE</sub> = 1200 V                                                                                                          | T <sub>C</sub> = 25°C                 | -    | _    | 250  | μΑ    |

|                                           |                      |                                                                                                                                   | T <sub>C</sub> = 125°C                | -    | 300  | -    | μΑ    |

|                                           |                      |                                                                                                                                   | T <sub>C</sub> = 150°C                | -    | _    | 3.5  | mA    |

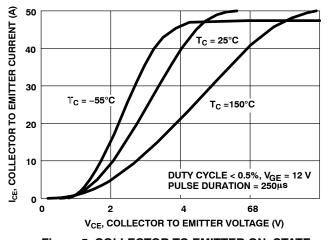

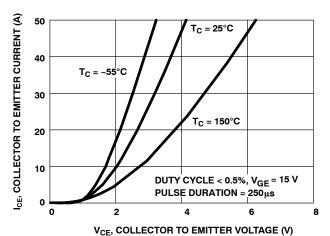

| Collector to Emitter Saturation Voltage   | V <sub>CE(SAT)</sub> | I <sub>C</sub> = 11 A,<br>V <sub>GE</sub> = 15 V                                                                                  | T <sub>C</sub> = 25°C                 | -    | 2.1  | 2.4  | V     |

|                                           |                      |                                                                                                                                   | T <sub>C</sub> = 150°C                | -    | 2.9  | 3.5  | V     |

| Gate to Emitter Threshold Voltage         | V <sub>GE(TH)</sub>  | $I_C = 90 \mu A, V_{CE} =$                                                                                                        | $I_C = 90 \mu A$ , $V_{CE} = V_{GE}$  |      | 6.8  | -    | V     |

| Gate to Emitter Leakage Current           | I <sub>GES</sub>     | $V_{GE}$ = ±20 V<br>$T_J$ = 150°C, $R_G$ = 10 $\Omega$ , $V_{GE}$ = 15 V, L = 400 $\mu$ H, $V_{CE(PK)}$ = 1200 V                  |                                       | -    | _    | ±250 | nA    |

| Switching SOA                             | SSOA                 |                                                                                                                                   |                                       | 55   | -    | -    | А     |

| Gate to Emitter Plateau Voltage           | V <sub>GEP</sub>     | I <sub>C</sub> = 11 A, V <sub>CE</sub> = 600 V                                                                                    |                                       | -    | 10.4 | -    | V     |

| On-State Gate Charge                      | Q <sub>G(ON)</sub>   | I <sub>C</sub> = 11 A,<br>V <sub>CE</sub> = 600 V                                                                                 | V <sub>GE</sub> = 15 V                | -    | 100  | 120  | nC    |

|                                           |                      |                                                                                                                                   | V <sub>GE</sub> = 20 V                | _    | 130  | 150  | nC    |

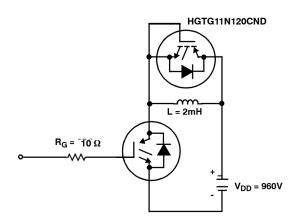

| Current Turn-On Delay Time                | t <sub>d(ON)I</sub>  | IGBT and Diode at $T_J$ = 25°C, $I_{CE}$ = 11 A, $V_{CE}$ = 960 V, $V_{GE}$ = 15 V, $R_G$ = 10 $\Omega$ ,                         |                                       | _    | 23   | 26   | ns    |

| Current Rise Time                         | t <sub>rl</sub>      |                                                                                                                                   |                                       | _    | 12   | 16   | ns    |

| Current Turn-Off Delay Time               | t <sub>d(OFF)I</sub> |                                                                                                                                   |                                       | _    | 180  | 240  | ns    |

| Current Fall Time                         | t <sub>fl</sub>      |                                                                                                                                   |                                       | _    | 190  | 220  | ns    |

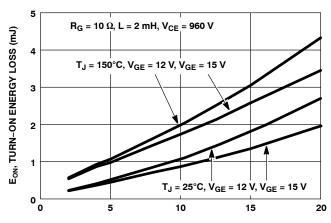

| Turn-On Energy                            | E <sub>ON</sub>      | ,                                                                                                                                 | L = 2 mH,<br>Test Circuit (Figure 20) |      | 0.95 | 1.3  | mJ    |

| Turn-Off Energy (Note 3)                  | E <sub>OFF</sub>     | Took official (Figur                                                                                                              |                                       |      | 1.3  | 1.6  | mJ    |

| Current Turn-On Delay Time                | t <sub>d(ON)I</sub>  | IGBT and Diode a                                                                                                                  | at T <sub>J</sub> = 150°C,            | _    | 21   | 24   | ns    |

| Current Rise Time                         | t <sub>rl</sub>      | I <sub>CE</sub> = 11 A,<br>V <sub>CF</sub> = 960 V,                                                                               |                                       | _    | 12   | 16   | ns    |

| Current Turn-Off Delay Time               | t <sub>d(OFF)I</sub> | V <sub>GE</sub> = 15 V,                                                                                                           |                                       | _    | 210  | 280  | ns    |

| Current Fall Time                         | t <sub>fl</sub>      | $R_G = 10 \Omega$                                                                                                                 | $R_G = 10 \Omega$ ,                   |      | 360  | 400  | ns    |

| Turn-On Energy                            | E <sub>ON</sub>      | L = 2 mH,<br>Test Circuit (Figure 20)                                                                                             |                                       | _    | 1.9  | 2.5  | mJ    |

| Turn-Off Energy (Note 3)                  | E <sub>OFF</sub>     |                                                                                                                                   |                                       | -    | 2.1  | 2.5  | mJ    |

| Diode Forward Voltage                     | V <sub>EC</sub>      | I <sub>EC</sub> = 11 A                                                                                                            |                                       | -    | 2.6  | 3.2  | V     |

| Diode Reverse Recovery Time               | t <sub>rr</sub>      | $I_{EC} = 11 \text{ A}, dI_{EC}/dt = 200 \text{ A/}\mu\text{s}$<br>$I_{EC} = 1 \text{ A}, dI_{EC}/dt = 200 \text{ A/}\mu\text{s}$ |                                       | -    | 60   | 70   | ns    |

|                                           |                      |                                                                                                                                   |                                       | -    | 32   | 40   | ns    |

| Thermal Resistance Junction To Case       | $R_{\theta JC}$      | IGBT                                                                                                                              |                                       | -    | _    | 0.42 | °C/W  |

|                                           |                      | Diode                                                                                                                             | Diode                                 |      | _    | 1.25 | °C/W  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

performance may not be indicated by the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

3. Turn–Off Energy Loss (E<sub>OFF</sub>) is defined as the integral of the instantaneous power loss starting at the trailing edge of the input pulse and ending at the point where the collector current equals zero (I<sub>CE</sub> = 0 A). All devices were tested per JEDEC Standard No. 24–1 Method for Measurement of Power Device Turn–Off Switching Loss. This test method produces the true total Turn–Off Energy Loss.

#### TYPICAL PERFORMANCE CHARACTERISTICS

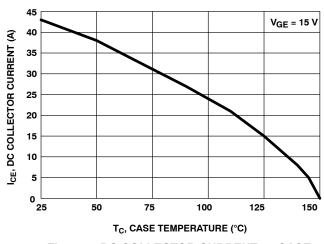

Figure 1. DC COLLECTOR CURRENT vs CASE TEMPERATURE

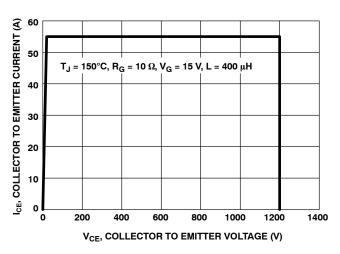

Figure 2. MINIMUM SWITCHING SAFE OPERATING AREA

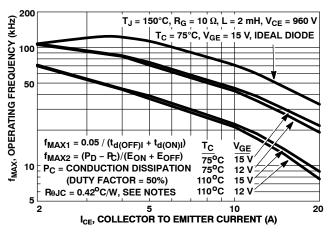

Figure 3. OPERATING FREQUENCY vs COLLECTOR

TO EMITTER CURRENT

Figure 4. SHORT CIRCUIT WITHSTAND TIME

Figure 5. COLLECTOR TO EMITTER ON-STATE VOLTAGE

Figure 6. COLLECTOR TO EMITTER ON-STATE VOLTAGE

#### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$\mathbf{I}_{\text{CE}},$  collector to emitter current (a)

Figure 7. TURN-ON ENERGY LOSS vs COLLECTOR TO EMITTER CURRENT

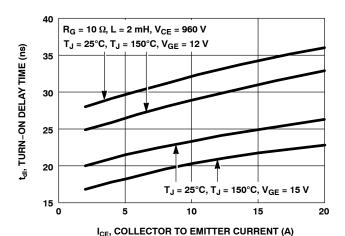

Figure 9. TURN-ON DELAY TIME vs COLLECTOR

TO EMITTER CURRENT

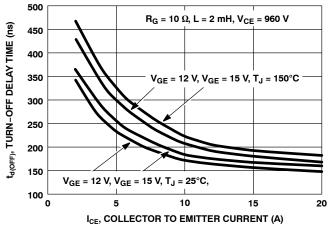

Figure 11. TURN-OFF DELAY TIME vs COLLECTOR

TO EMITTER CURRENT

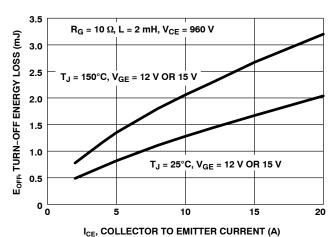

Saura & TUDN OFF ENERGY LOSS ...

Figure 8. TURN-OFF ENERGY LOSS vs COLLECTOR TO EMITTER CURRENT

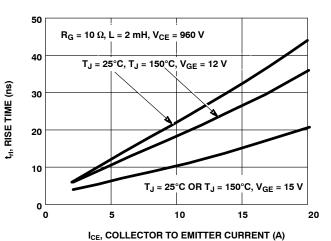

Figure 10. TURN-ON RISE TIME vs COLLECTOR

TO EMITTER CURRENT

ICE, COLLECTOR TO EMITTER CURRENT (A)

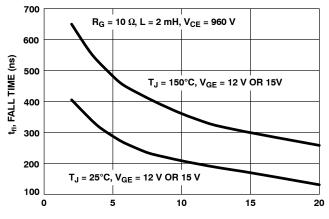

Figure 12. FALL TIME vs COLLECTOR TO EMITTER CURRENT

+

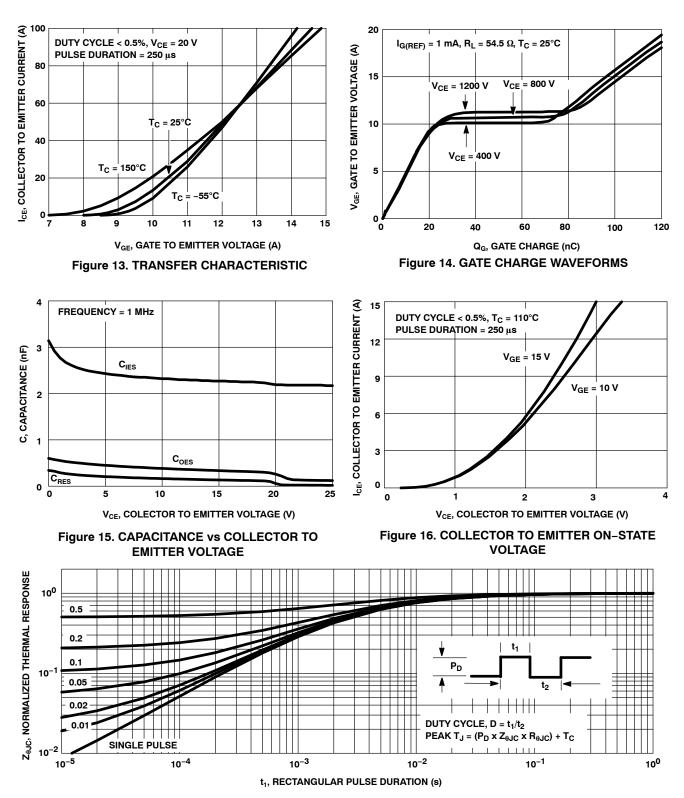

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Figure 17. NORMALIZED TRANSIENT THERMAL RESPONSE, JUNCTION TO CASE

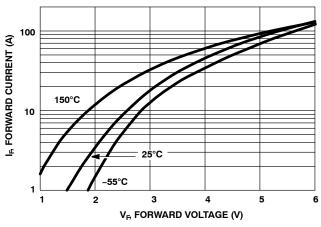

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Figure 18. DIODE FORWARD CURRENT vs FORWARD VOLTAGE DROP

Figure 19. RECOVERY TIMES vs FORWARD CURRENT

#### **TEST CIRCUITS AND WAVEFORMS**

Figure 20. Inductive Switching Test Circuit

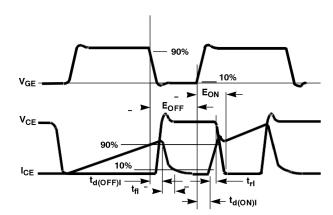

Figure 21. SWITCHING TEST WAVEFORMS

#### HANDLING PRECAUTIONS FOR IGBTS

Insulated Gate Bipolar Transistors are susceptible to gate-insulation damage by the electrostatic discharge of energy through the devices. When handling these devices, care should be exercised to assure that the static charge built in the handler's body capacitance is not discharged through the device. With proper handling and application procedures, however, IGBTs are currently being extensively used in production by numerous equipment manufacturers in military, industrial and consumer applications, with virtually no damage problems due to electrostatic discharge. IGBTs can be handled safely if the following basic precautions are taken:

- Prior to assembly into a circuit, all leads should be kept shorted together either by the use of metal shorting springs or by the insertion into conductive material such as "ECCOSORBD™ LD26" or equivalent

- When devices are removed by hand from their carriers, the hand being used should be grounded by any suitable means – for example, with a metallic wristband

- 3. Tips of soldering irons should be grounded

- 4. Devices should never be inserted into or removed from circuits with power on

- 5. Gate Voltage Rating Never exceed the gate–voltage rating of  $V_{\text{GEM}}$ . Exceeding the rated  $V_{\text{GE}}$  can result in permanent damage to the oxide layer in the gate region

- 6. Gate Termination The gates of these devices are essentially capacitors. Circuits that leave the gate open– circuited or floating should be avoided. These conditions can result in turn–on of the device due to voltage buildup on the input capacitor due to leakage currents or pickup

- Gate Protection These devices do not have an internal monolithic Zener diode from gate to emitter. If gate protection is required an external Zener is recommended

#### **OPERATING FREQUENCY INFORMATION**

Operating frequency information for a typical device (Figure 3) is presented as a guide for estimating device performance for a specific application. Other typical frequency vs collector current ( $I_{CE}$ ) plots are possible using the information s11hown for a typical unit in Figures 5, 6, 7, 8, 9 and 11. The operating frequency plot (Figure 3) of a typical device shows  $f_{MAX1}$  or  $f_{MAX2}$ ; whichever is smaller at each point. The information is based on measurements of a typical device and is bounded by the maximum rated junction temperature.

$f_{MAX1}$  is defined by  $f_{MAX1}=0.05/(t_{d(OFF)I}+t_{d(ON)I}).$  Deadtime (the denominator) has been arbitrarily held to 10% of the on–state time for a 50% duty factor. Other definitions are possible.  $t_{d(OFF)I}$  and  $t_{d(ON)I}$  are defined in Figure 21. Device turn–off delay can establish an additional frequency limiting condition for an application other than  $T_{JM}.\ t_{d(OFF)I}$  is important when controlling output ripple under a lightly loaded condition.

$f_{MAX2}$  is defined by  $f_{MAX2}$  =  $(P_D - P_C)/(E_{OFF} + E_{ON}).$  The allowable dissipation  $(P_D)$  is defined by  $P_D$  =  $(T_{JM} - T_C)/R_{\theta JC}.$  The sum of device switching and conduction losses must not exceed  $P_D.$  A 50% duty factor was used (Figure 3) and the conduction losses  $(P_C)$  are approximated by

$$P_{C} = (V_{CE} \times I_{CE})/2$$

(eq. 1)

$E_{ON}$  and  $E_{OFF}$  are defined in the switching waveforms shown in Figure 21.  $E_{ON}$  is the integral of the instantaneous power loss ( $I_{CE} \times V_{CE}$ ) during turn—on and  $E_{OFF}$  is the integral of the instantaneous power loss ( $I_{CE} \times V_{CE}$ ) during turn—off. All tail losses are included in the calculation for  $E_{OFF}$ ; i.e., the collector current equals zero ( $I_{CE} = 0$ ).

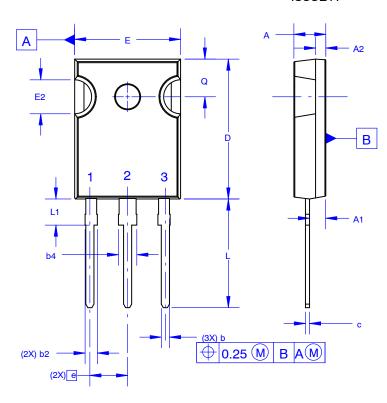

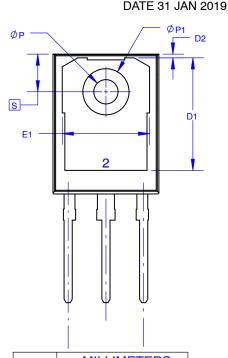

#### TO-247-3LD SHORT LEAD

CASE 340CK ISSUE A

- A. DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSIONS.

- B. ALL DIMENSIONS ARE IN MILLIMETERS.

- C. DRAWING CONFORMS TO ASME Y14.5 2009.

- D. DIMENSION A1 TO BE MEASURED IN THE REGION DEFINED BY L1.

- E. LEAD FINISH IS UNCONTROLLED IN THE REGION DEFINED BY L1.

# GENERIC MARKING DIAGRAM\*

XXXX = Specific Device Code

A = Assembly Location

Y = Year

WW = Work Week

ZZ = Assembly Lot Code

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

| DIM   | MILLIMETERS |       |       |  |  |  |

|-------|-------------|-------|-------|--|--|--|

| DIIVI | MIN         | NOM   | MAX   |  |  |  |

| Α     | 4.58        | 4.70  | 4.82  |  |  |  |

| A1    | 2.20        | 2.40  | 2.60  |  |  |  |

| A2    | 1.40        | 1.50  | 1.60  |  |  |  |

| b     | 1.17        | 1.26  | 1.35  |  |  |  |

| b2    | 1.53        | 1.65  | 1.77  |  |  |  |

| b4    | 2.42        | 2.54  | 2.66  |  |  |  |

| С     | 0.51        | 0.61  | 0.71  |  |  |  |

| D     | 20.32       | 20.57 | 20.82 |  |  |  |

| D1    | 13.08       | ~     | ~     |  |  |  |

| D2    | 0.51        | 0.93  | 1.35  |  |  |  |

| E     | 15.37       | 15.62 | 15.87 |  |  |  |

| E1    | 12.81       | ~     | ~     |  |  |  |

| E2    | 4.96        | 5.08  | 5.20  |  |  |  |

| е     | ~           | 5.56  | ~     |  |  |  |

| L     | 15.75       | 16.00 | 16.25 |  |  |  |

| L1    | 3.69        | 3.81  | 3.93  |  |  |  |

| ØΡ    | 3.51        | 3.58  | 3.65  |  |  |  |

| ØP1   | 6.60        | 6.80  | 7.00  |  |  |  |

| Q     | 5.34        | 5.46  | 5.58  |  |  |  |

| S     | 5.34        | 5.46  | 5.58  |  |  |  |

| DOCUMENT NUMBER: | 98AON13851G           | Electronic versions are uncontrolled except when accessed directly from the Document Repository. Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | TO-247-3LD SHORT LEAD |                                                                                                                                                                                  | PAGE 1 OF 1 |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems. or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales